ESD保护二极管的PN 结结构(如平面型、沟槽型)如何影响其ESD泄放能力?

1.平面型 PN 结:

PN结位于芯片表面,结面积易做大,可承受更大的ESD脉冲电流(如:HBM 15kV),但寄生电容较大(因结面积大),且表面易受污染物影响导致击穿电压不稳定,适用于低频、大电流防护场景(如:电源VBUS)

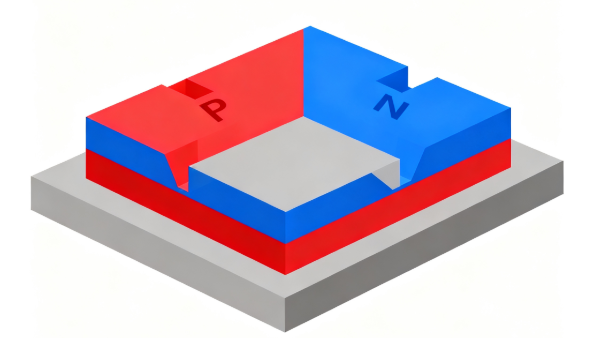

1.1 平面型 PN 结是一种通过平面工艺(如光刻、扩散或离子注入)在半导体晶片表面形成的 PN 结结构

其核心特点是整个PN 结平面化地分布在硅片表面,并通过二氧化硅(SiO₂)氧化层实现保护和隔离,这与早期的点接触型或台面型 PN 结形成鲜明对比

-

- 氧化层生长:在 N 型硅衬底表面热生长一层二氧化硅(SiO₂),作为后续工艺的掩蔽层

- 光刻定义区域:通过光刻技术在氧化层上刻蚀出窗口,暴露出需要掺杂的区域。例如,若要形成 P 型区,需在窗口处注入或扩散硼(B)等受主杂质

- 选择性掺杂:杂质通过扩散或离子注入进入暴露的硅表面,在硅片内部形成 P 型区,与原始 N 型衬底交界处即形成 PN 结

- 金属电极制备:最后通过光刻和蒸镀工艺在 P 区和 N 区表面分别沉积金属(如铝)电极,实现外部电气连接

氧化层的关键作用

-

- 杂质掩蔽:未被光刻窗口暴露的氧化层可阻挡杂质扩散,确保 PN 结仅在目标区域形成

- 表面钝化:氧化层覆盖 PN 结表面,减少表面缺陷和漏电流,显著提升器件稳定性和可靠性

- 绝缘隔离:氧化层作为天然绝缘体,可在集成电路中隔离相邻器件,避免短路

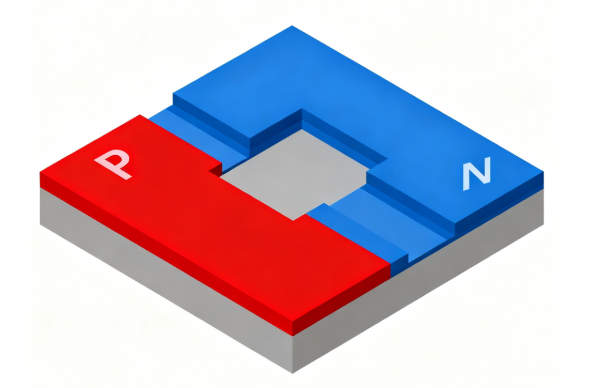

- 台面型 PN 结

-

- 结构:通过蚀刻形成 “台阶状” 结构,PN 结暴露于侧面,需额外钝化层保护

- 优势:电场分布更均匀,耐压能力强(可达数千伏),适用于高压器件(如功率二极管)

- 劣势:工艺复杂、成本高,且因侧面暴露导致漏电流较大

- 点接触型 PN 结

-

- 结构:通过金属丝与半导体表面点接触形成,PN 结面积极小(如微米级)

- 优势:结电容小(<1pF),适合高频检波或小信号处理

- 劣势:无法承受大电流,稳定性较差

-

- 高电流承载能力:平面型 PN 结的接触面积大(可达平方毫米级),可通过数安培至数十安培的电流,例如快速二极管和功率整流器。

- 低漏电流与高稳定性:氧化层的钝化作用显著降低表面漏电流,长期工作可靠性高。

- 适合大规模集成:平面工艺与集成电路制造兼容,可在同一硅片上密集排列大量 PN 结(如芯片中的二极管阵列)。

-

- 整流电路:如 AC-DC 电源中的桥式整流器,利用平面型二极管的大电流能力。

- 开关器件:在数字电路中作为高速开关,响应速度可达纳秒级。

- 传感器与光电器件:如平面型光电二极管,通过大面积 PN 结提高光吸收效率

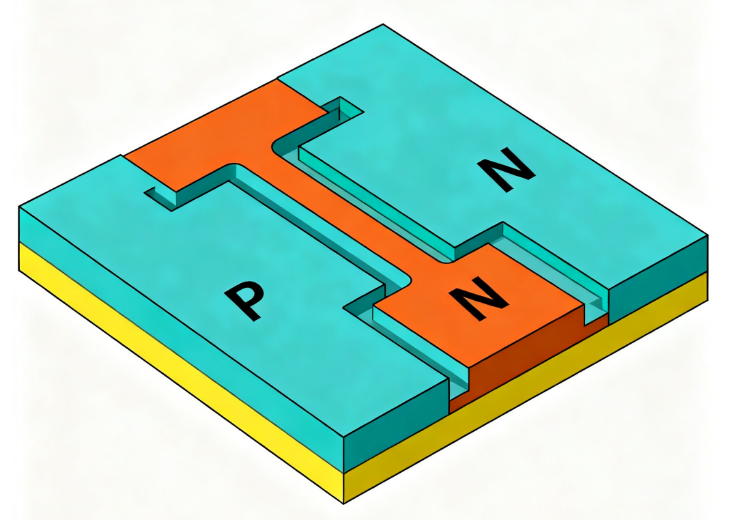

2.沟槽型 PN 结:

通过深沟槽隔离技术将PN结垂直分布于芯片内部,结边缘电场更均匀,击穿电压一致性更好,且结面积可精准控制,寄生电容比平面型低30%-50%(如:<0.5pF),但结面积受沟槽深度限制,电流泄放能力略弱于平面型,适用于高频信号通路(如HDMI 2.1、DisplayPort)

2.1.1 平面工艺的核心步骤

平面型 PN 结的制造基于光刻-扩散技术:

-

- 氧化层生长:在N型硅衬底表面热生长一层二氧化硅(SiO₂),作为后续工艺的掩蔽层

- 光刻定义区域:通过光刻技术在氧化层上刻蚀出窗口,暴露出需要掺杂的区域。例如,若要形成P型区,需在窗口处注入或扩散硼(B)等受主杂质

- 选择性掺杂:杂质通过扩散或离子注入进入暴露的硅表面,在硅片内部形成P型区,与原始N型衬底交界处即形成PN结

- 金属电极制备:最后通过光刻和蒸镀工艺在P区和N区表面分别沉积金属(如铝)电极,实现外部电气连接

2.1.2 氧化层的关键作用

-

-

- 杂质掩蔽:未被光刻窗口暴露的氧化层可阻挡杂质扩散,确保PN结仅在目标区域形成

- 表面钝化:氧化层覆盖PN结表面,减少表面缺陷和漏电流,显著提升器件稳定性和可靠性

- 绝缘隔离:氧化层作为天然绝缘体,可在集成电路中隔离相邻器件,避免短路

2.2.1 台面型PN结

-

- 结构:通过蚀刻形成 “台阶状” 结构,PN结暴露于侧面,需额外钝化层保护

- 优势:电场分布更均匀,耐压能力强(可达数千伏),适用于高压器件(如功率二极管)

- 劣势:工艺复杂、成本高,且因侧面暴露导致漏电流较大

2.2.2 点接触型PN结

-

- 结构:通过金属丝与半导体表面点接触形成,PN 结面积极小(如微米级)

- 优势:结电容小(<1pF),适合高频检波或小信号处理

- 劣势:无法承受大电流,稳定性较差

3.1.1 性能优势

-

- 高电流承载能力:平面型 PN 结的接触面积大(可达平方毫米级),可通过数安培至数十安培的电流,例如快速二极管和功率整流器

- 低漏电流与高稳定性:氧化层的钝化作用显著降低表面漏电流,长期工作可靠性高

- 适合大规模集成:平面工艺与集成电路制造兼容,可在同一硅片上密集排列大量PN结(如芯片中的二极管阵列)

ESD 参数:https://www.yint.com.cn/products/emsproduct/esd/index.html

ESD保护二极管的雪崩击穿与齐纳击穿在物理机制上差异?

热门新闻

热门新闻